# 基於FPGA的單晶片雙8051雙機熱備系統設計與實現 Design and Realization of FPGA Based Single-Chip Dual-Core Embedded Dual **Module Hot Spare Syste**

李翔 Xiang Li, 戴勝華 Sheng-Hua Dai, 邊興田 Xing-Tian Bian 北京交通大學自控系 ariesmuu@tom.com, dsh@bjtu.edu.cn, 07120292@bjtu.edu.cn

## 摘要

本文提出了一種單晶片多微控制器(Micro Controller Unit, MCU)系統的設計方法,並給出了基 於現場可編程門陣列 (Field Programmable Gate Array, FPGA) 的單晶片雙軟核雙機熱備多通道電壓檢測系統 的設計方案,並詳細介紹通過Actel Fusion StartKit數模 混合FPGA的實現方法。

關鍵字:單晶片雙軟核、FPGA、Core8051軟核、雙機 熱備。

### **Abstract**

This paper mentions a method of designing singlechip multi-core system, gives a scheme of FPGA (Field Programmable Gate Array) based single-chip dual-core DMHS (dual module hot spare) system which detects multi-channel voltage, and explicates the realization with Actel Fusion StarKit FPGA.

Keywords: Single-chip Dual-core, FPGA, Core8051,

## 1引言

電腦技術的發展已經進入後PC時代,無論是在民 用電子消費品領域還是軍工業領域,嵌入式系統都有 極其廣闊的應用和發展空間。在某些特定領域(例如 航空航天、軌道交通、地質勘探、軍事應用等),實 際應用對嵌入式系統的安全性和可靠性提出了很高的 要求,雙機熱備系統是一種成熟的解決方案。

雙機熱備系統由兩個硬體結構完全相同的子單元 組成,分別為工作單元和備用單元。雙單元同步獨立 工作,而系統的輸出只選取工作單元的輸出。當單機 發生故障時,進入維修狀態,系統輸出切換至當前工 作單元的輸出。雙機熱備系統的優點是單機故障或維 修時,不影響整個系統的使用,在保證系統安全的前 提下,使系統的可用性得到極大的提升。而熱備功能 的實現可以有效地使整個系統正常工作的持續能力即 可靠性得到明顯的改善。

以往的雙機熱備系統在硬體設計上通常採用兩塊 MCU晶片架構的模式,對於嵌入式系統而言,雙晶片

模型功耗比單晶片大,周邊器件和設備擴展繁多、電 路佈局複雜,這都會對系統的可靠性和安全性造成不 良影響,並且增加了額外的系統開銷和能耗。本文介 紹一種在單晶片嵌入兩個獨立的MCU軟核實現雙機熱 備系統的方法,以及通過Actel Fusion StartKit數模混合 FPGA實現的方法,並完成多通道類比電壓的採集。

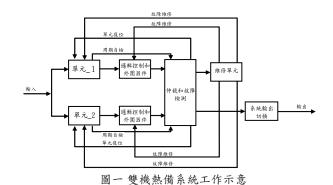

## 2 雙機熱備系統工作模式

雙機熱備系統中兩個子單元具有完全相同的硬體 結構,兩個單元開機後同步獨立工作,系統選取工作 單元的輸出為系統輸出。當備用單元發生故障時,系 統輸出仍為工作單元的輸出,而備用單元進入維修狀 態;維修結束後,備用單元通過日誌更新機制和工作 單元實現同步,並繼續作為系統的備用單元;當工作 單元發生故障時,系統輸出切換至備用單元的輸出, 備機轉為主機,主機進行維修,維修結束後通過日誌 更新和備機同步,然後作為備機使用;如果發生工作 單元和備用單元同時無法工作的狀況(故障、維修或 待修),則系統故障,無法繼續進行工作。除了系統 輸出的自動切換,系統也可以進行手動切換。由於兩 個單元的硬體結構完全相同並且運行相同的程式,所 以手動切換不影響系統的工作。雙機熱備系統工作示 意如圖一所示:

Figure 1. Operation of DMHS System

導致系統或單元故障的因素有很多,例如:單元 的輸出故障、工作單元和備用單元不同步、周邊器件 和設備故障等等。為了針對不同的故障進行維修,必 須分門別類地檢測出各種故障。面向不同的應用場合 需求,對於故障檢測和維修的要求也不盡相同。

## 3系統硬體總體實現

在FPGA中嵌入軟核時首先要考慮的制約條件是FPGA的門電路數量,只有擁有足夠多門電路,才能容納下多個MCU軟核和其他外設的IP核。特別是對於MCU軟核,使用的門陣列數量較多,要考慮好FPGA晶片的選型。其次,考量其他硬體資源如:時鐘、鎖相環(Phase Locked Loop, PLL)、隨機存取記憶體(Random-Access Memory, RAM)、唯讀記憶體(Read-Only Memory, ROM)等,無論是FPGA內部提供,還是周邊器件提供,都必須能支援設計的需要。

綜合上面的標準,本文設計選擇Actel的Fusion StartKit數模混合FPGA實現雙機熱備系統。Actel的Fusion StartKit數模混合FPGA擁有600萬門門陣列,片內集成了Flash Memory、RAM、先入先出數據存儲器(First In First Out, FIFO)和類比模組;片外提供48MHz的晶振,可以通過2個PLL模組分頻出6個0.75MHz~350MHz;支持Core8051軟核的嵌入,通過Core8051網表檔和時鐘、資料記憶體、程式記憶體的載入,實現完整的8051單片機。該FPGA上集成有類比模組,包括ADC和類比Quad兩部分,可進行32通道8、10、12位元精度的電壓採集,本文示例性地進行兩路8位元精度的電壓採集後輸出,通過板載的LCD1602顯示採樣結果。本文的重點內容在於介紹在單晶片中嵌入雙Core8051軟核,並遵循雙機熱備模式工作,完成系統切換、故障檢測和日誌更新。

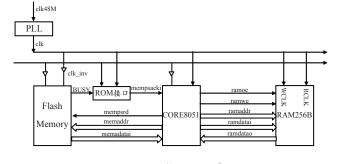

## 3.1 雙Core8051的嵌入

雙機熱備系統要求系統的兩個單元硬體結構完全相同,本文中在單晶片FPGA中嵌入兩個獨立的8051單片機。Core8051內核使用Core8051網表檔完成8051的介面和內部結構聲明;片外的48MHz晶振經PLL模組分頻出兩個10MHz作為兩個8051的系統時鐘;從片內RAM中分別劃分出兩組256B空間作為兩個8051的內部資料記憶體,片內Flash Memory提供兩個64KB的空間作為8051的程式記憶體。建立好的每個8051單元組成如圖二所示:

圖二 完整的8051單元組成 Figure 2. Constitution of A Complete 8051 Unit

RAM塊的讀寫時序符合core8051讀寫時序,所以不需要介面,直接將RAM掛到總線上即可。但是由於

Flash Memory在正常模式下,只要在塊與塊之間跳轉時就會出現四個時鐘(Clock, CLK)週期的Busy信號,並且在8051發出讀命令讀0000H這個位址資料時,Busy信號也會有效,但這時並不是四個CLK週期,只有一個時鐘週期,這將導致core8051讀不到0000H這個單元的資料,因此在core8051和Flash Memory間添加一個轉化控制時序的介面,使之能正常通信。單片機的程式燒寫至Flash Memory中。

#### 3.2 雙機熱備的實現

系統切換是雙機熱備系統首要的功能要求,當工 作單元出現故障時,要求進行系統切換,這裏示範性 地給出兩種故障檢測方式。

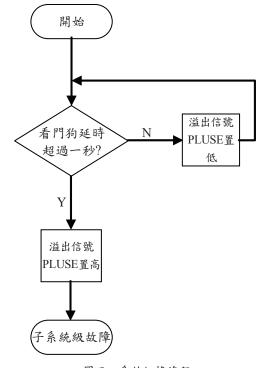

首先為兩個8051分別設置兩個看門狗計時器,要求兩個8051向各自的看門狗發送週期自檢信號。若看門狗在溢出前收到該信號則單元正常工作,否則溢出,該單元判為故障,若備用單元正常,系統輸出切換至備用單元輸出。

其次將ADC轉換結果和系統輸出結果進行比較, 若相同,系統正常,否則判為故障,若備用單元正 常,系統輸出切換至備用單元輸出。

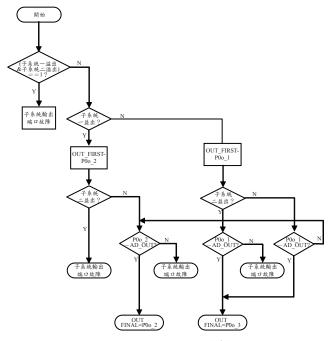

系統切換通過下述語句實現 assign OUT\_FIRST=(PLUSE\_1 && PLUSE\_2)? 8'bz:((PLUSE 1)?P0o 2:P0o 1)

assign OUT\_FINAL=(AD\_OUT[11:4]==OUT\_FIRST)? OUT\_FIRST:(((PLUSE 1 && PLUSE 2)==0)?P0o\_2:8'bz)

PLUSE為兩個看門狗的溢出信號,P00為兩個8051的P0輸出口,OUT\_FIRST是比較前的輸出,OUT\_FINAL是比較後的系統輸出,它們的判斷如圖三所示:

圖三 系統切換流程 Figure 3. System Switch Flows

系統切換流程(續)

Figure 3. System Switch Flows (Continued)

#### 3.3 日誌更新

故障的單元復位後,為了使自己與工作單元同 步,需要進行日誌更新。日誌更新的資料通信是通過 兩個Core8051間的串口通信實現的,所以將兩個8051 的串口發送端與輸出端對接起來。在8051的程式裏, 有兩個外部中斷服務程式,INTO是串口的發送服務, INT1是串口的接收服務。

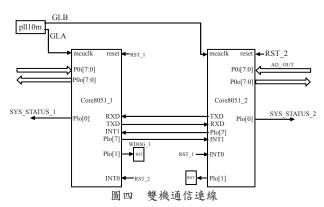

8051的外部中斷0和對應側8051的復位信號相連, P1.7和對應側8051的外部中斷INT1相連,即單元修復 後,通過串口通信進行日誌更新。將外部中斷INTO設 置為邊沿觸發,當備機復位後,會有一個下降沿送到 主機的INTO口,於是主機開始執行外部中斷INTO服 務程式。在INTO服務程式的開始,首先通過P1.7向備 機發送一個下降沿信號,然後通過串口進行資料的發 送。而此時備機的INT1口接到觸發信號,開始執行外 部中斷INT1服務程式。外部中斷INT1的內容即接收串 口資料,同時將資料通過PO輸出。雙機間的連線示意 如圖四所示。

Figure 4. Connections Between Two Systems

## 4 結語

嵌入式系統在應用領域發展迅速,隨著FPGA技 術的進步,單晶片內的邏輯門電路數量更多,軟核的 編寫更加成熟,這使得在單晶片中嵌入多個MCU成為 可能。單晶片的優勢在於功耗更小,電路設計更加便 捷,系統可靠性和安全性更高,這就展現了單晶片多 核系統廣闊的發展和應用空間。本文提出一種在FPGA 中嵌入雙Core8051軟核實現雙機熱備系統並進行即時多 通道電壓採集的方法,並通過選定開發板實現。在單 晶片中嵌入多軟核,能夠大大擴展嵌入式系統應用的 廣度和深度。

本文的特色在於:恰當利用單晶片有限的資源, 嵌入兩個成熟的Core8051軟核,遵循雙機熱備系統的工 作原理,合理實現系統切換、故障檢測、日誌更新, 雙機通信和系統切換經綜合後燒入運行順暢無阻,對 在單晶片中嵌入多MCU軟核並協調其工作做出了一次 新的嘗試。無論是對稱式還是非對稱式多核系統,單 晶片無疑是一種全新的解決方案。

# 參考文獻

- [1] 周立功等, Actel FPGA實驗教程——基於Fusion StartKit開發板[M],廣州致遠電子有限公司, 2007 •

- 周立功等,Actel FPGA原理與應用——基於Fusion [2] StartKit 系列[M] ,廣州致遠電子有限公司,2007。

- [3] 夏宇聞, Verilog數位系統設計教程[M], 北京航空 航天大學出版社,2003。

- [4] 戴勝華等,單片機原理與應用[M],北京交通大 學出版社,2005。

# 作者簡介

李翔 (Xiang Li) 北京交通大學自控系 在讀碩士。主要研究領域為嵌入式系統 軟體和硬體、監測系統等。

戴勝華 (Sheng-hua Dai) 北京交通大學 自控系副教授。主要研究方向為嵌入式 系統、微機監測、鐵路信號等。

# 440 國立宜蘭大學電機資訊學院學報 創刊號 Journal of Internet Technology Volume 9 (2008) NO.5

邊興田(Xing-tian Bian)北京交通大學 自控系在讀碩士。主要研究領域為嵌入 式系統軟體和硬體、監測系統等。